Logic Gate Delay Modeling -1 Bishnu Prasad Das Research Scholar CEDT, IISc, Bangalore - ppt download

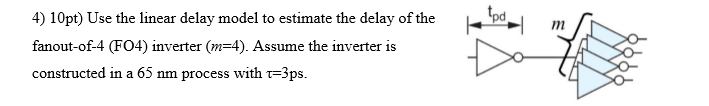

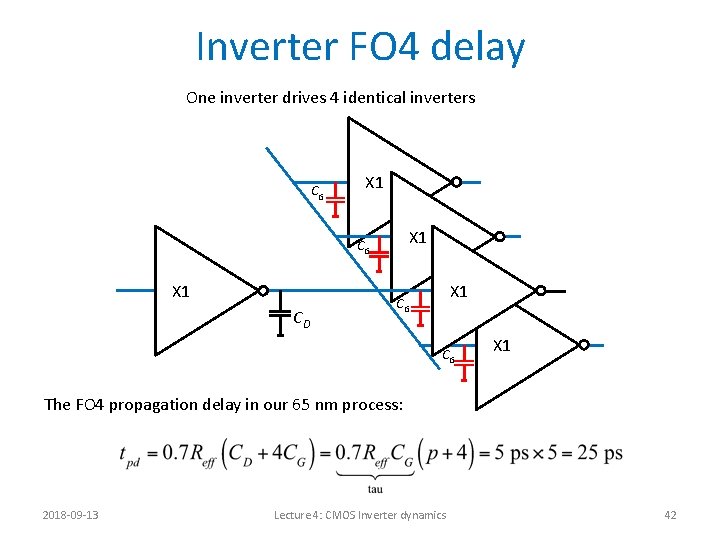

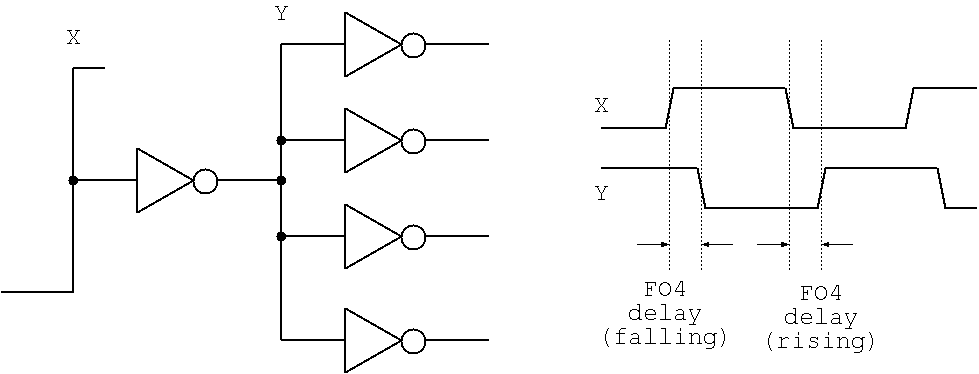

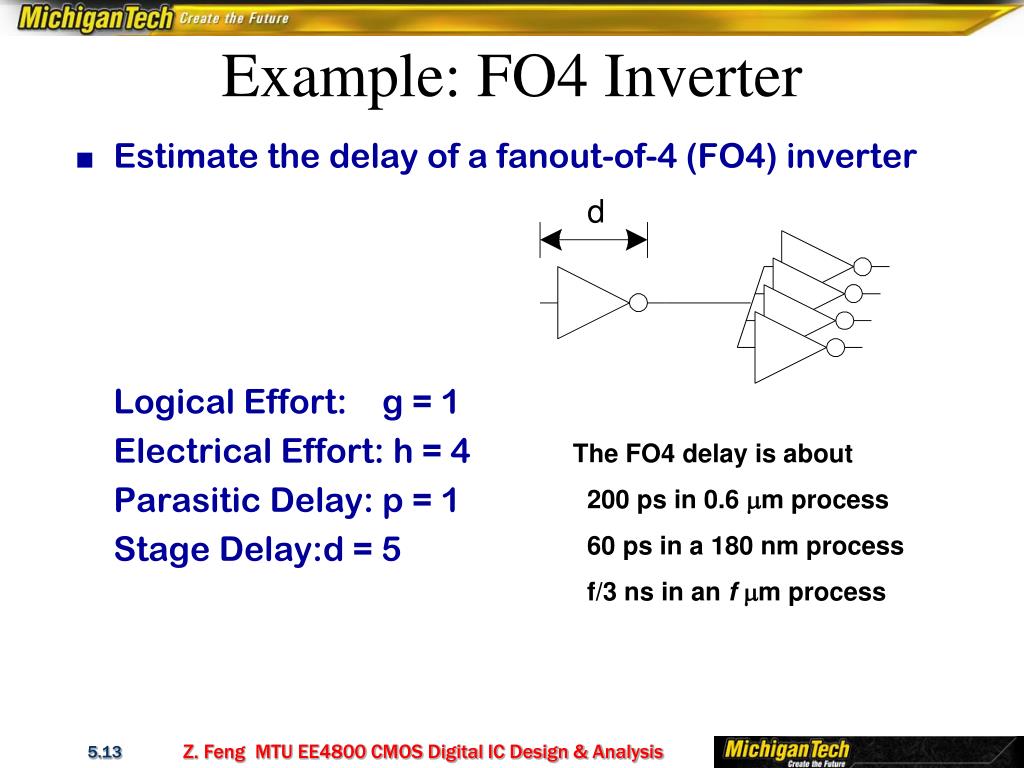

e.g. τ = 12 ps in 180nm, 40 ps in 0.6 µm Delay has two components where, f = Effort Delay (stage effort)= gh p =Parasitic Delay - PDF Free Download

PPT - The Optimal Logic Depth Per Pipeline Stage is 6 to 8 FO4 Inverter Delays PowerPoint Presentation - ID:9436430

![The Stuff Dreams Are Made Of [Part 2] The Stuff Dreams Are Made Of [Part 2]](http://www.realworldtech.com/includes/images/articles/cmosintro2-fig3.gif?x56147)

![PDF] The optimal logic depth per pipeline stage is 6 to 8 FO4 inverter delays | Semantic Scholar PDF] The optimal logic depth per pipeline stage is 6 to 8 FO4 inverter delays | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/b29a6f1098b1b031f549dc65cbf77108ca9858d6/3-Figure3-1.png)

![PDF] The optimal logic depth per pipeline stage is 6 to 8 FO4 inverter delays | Semantic Scholar PDF] The optimal logic depth per pipeline stage is 6 to 8 FO4 inverter delays | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/b29a6f1098b1b031f549dc65cbf77108ca9858d6/3-Table1-1.png)